Honest question coming from a point of consumer-thinking ignorance: With GPU makers putting out x8 cards on PCIe 4.0 and the heat issues with PCIe 5.0 SSDs, what practical nonenterprise uses are these speeds going to have?

Still waiting on direct storage to start coming to PC games so games can start benefiting from this type of hardware.

what practical nonenterprise uses are these speeds going to have?

None. These are very much enterprise-oriented updates. These extreme speeds are so difficult to achieve that it outweighs the simplification of scaling down the number of lanes. It’s better to use a PCIe 5.0 x16 connection than PCIe 7.0 x4 in consumer hardware.

I’m not sure I even care, I just want it!

A 10TB NVME running at PCIE 7 X16 would feel like actual magic. Stuff would load before you’d even lifted your finger up off the mouse. I can imagine that processors no matter what they are would become the bottle neck and not the IO. Bring it onThat would be faster than the RAM on most systems!

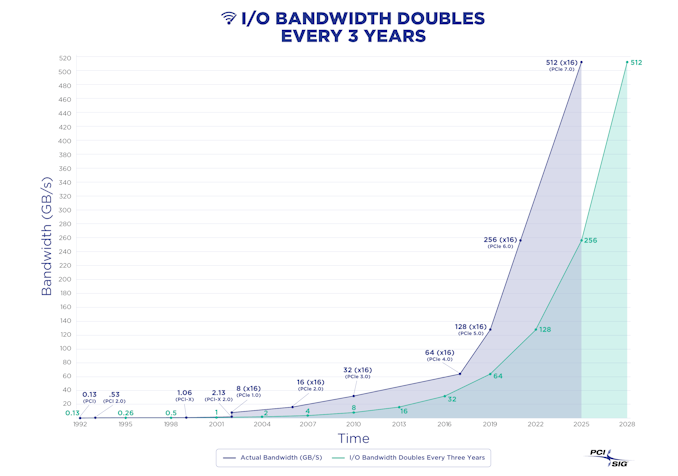

We seem to have skipped 6?

The PCIe 6 spec was finalized in early 2022 but - despite most every article saying to expect PCIe 6 hardware w/in 12-18 months of the finalization (which is right about now) I haven’t seen anything out there for sale yet. Perhaps it’s just going to be one of those PCIe generations that won’t gain much traction.

For a single device there’s really no benefit right now, but there is a huge benefit for aggregate bandwidth. Your typical consumer motherboard/CPU doesn’t actually have a ton of lanes, most lanes are provided by the PCH, meaning you’re actually sharing bandwidth for a lot of devices. Typically only one x16 slot (for GPU) and an NVME slot are connected directly to the CPU. With PCIe-6.0 and beyond you can break those lanes into more lower speed lanes and not have to share bandwidth.

I was thinking about how ~24 lanes would start feeling a lot more generous, but I also feel like narrowing lanes per slot would mean faster obsolescence. Let’s say I get a PCIe 5.0 x4 SSD in two years that survives long enough for 6.0 to be mainstream on a new board … but x2 is now standard for SSDs to share the lanes better overall. Isn’t that now effectively a 5.0 x2 drive?

Ultimately depends on how the motherboard manufacturers implement it and the choices they provide. If they were smart they wouldn’t narrow lanes, but instead break up most of the higher speed lanes into multiple lower speed ones.

Just as an example, that x16 lane slot to the CPU, with PCIe-6.0 you could break it up into three 4.0x16 slots and four 4.0x4 NVME slots.

Granted, at PCIe-6.0 your probably well beyond the total bandwidth a normal user would need. At that point you hope as the technology matures so it can reduce costs by reducing how many lanes a CPU and motherboard need at all.

Ah … I didn’t realize “downscaling” (there’s a better term I’m sure) at the motherboard level to older generations was a thing. Wait. Is that already a thing with some of the 5.0/4.0 boards?

Yes, that’s what they have been doing for quite a while now.

The chipset splits a few PCIe lanes from the CPU into many PCIe lanes for lower speed devices to use. Of course those lanes all share the same bandwidth with each other and with the USB and SATA ports in the chipset.